Coreboot debugging, configuration, tint, etc.

Coreboot provides a lot of possibilities of configurations, primary and secondary payloads and debugging mechanisms.

In the coreboot git make the following configuration.

$ make menuconfig $ touch bootorder.txt

General setup

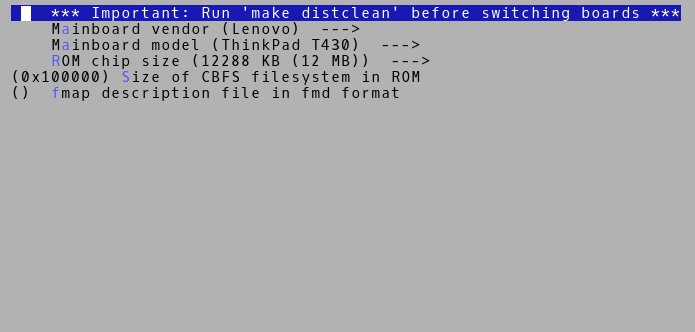

Mainboard

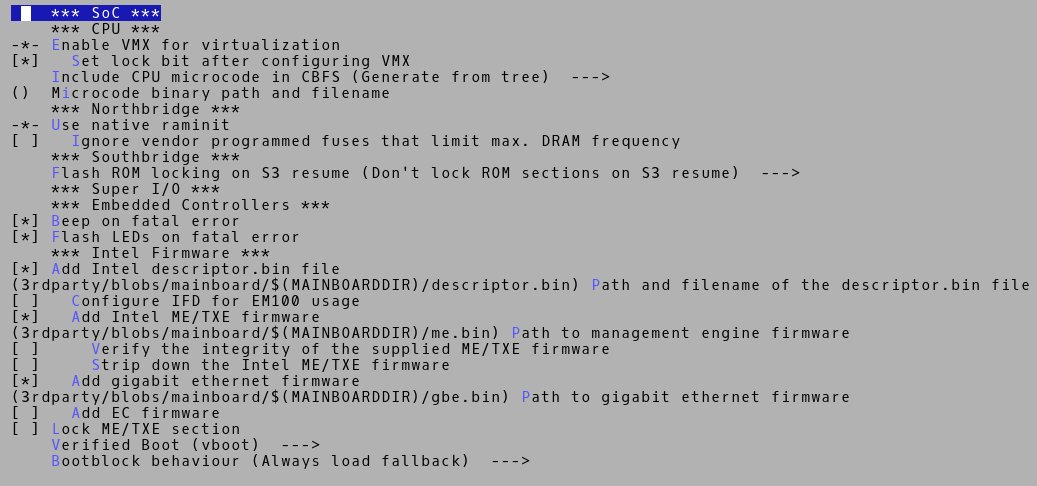

Chipset

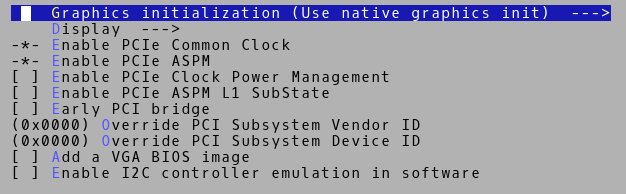

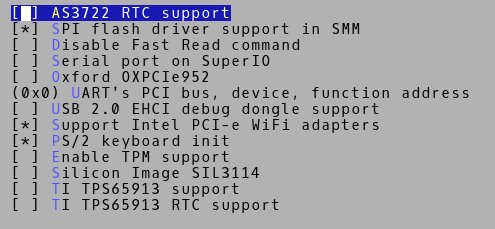

Devices

Generic Drivers

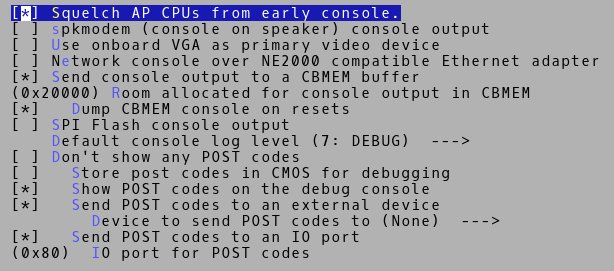

Console

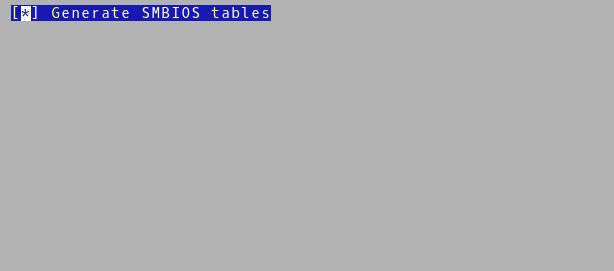

System tables

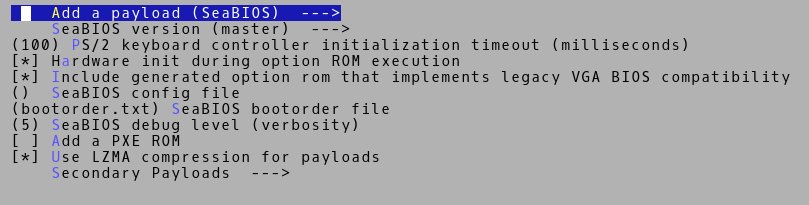

Payload

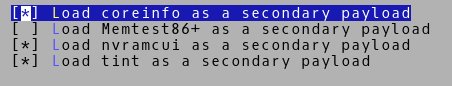

Secondary Payloads

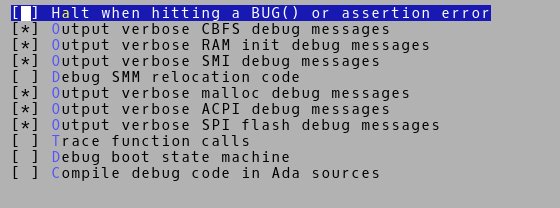

Debugging

To get necessary information to set the boot order. The cbmem tool is used to read the debug information after the coreboot has booted on the device.

Change to the util/cbmem in the coreboot git. (See previous post)

$ cd ~/coreboot/util/cbmem

Build the tool.

make

Read from the debug messages and grep for bootorder entries.

sudo ./cbmem -c | grep bootorder -A 1 Searching bootorder for: /pci@i0cf8/pci-bridge@1c/*@0 Found 0 lpt ports -- Searching bootorder for: /rom@img/tint Searching bootorder for: /rom@img/coreinfo Discarding ps2 data 0f (status=11) Searching bootorder for: /pci@i0cf8/*@1f,2/drive@1/disk@0 AHCI/1: registering: "DVD/CD [AHCI/1: PLDS DVD-RW DS8A8SH ATAPI-8 DVD/CD]" -- Searching bootorder for: /pci@i0cf8/usb@1d/hub@1/storage@1/*@0/*@0,0 Searching bootorder for: /pci@i0cf8/usb@1d/hub@1/usb-*@1 Searching bootorder for: /pci@i0cf8/*@1f,2/drive@0/disk@0 AHCI/0: Set transfer mode to UDMA-6 -- Searching bootorder for: HALT

Insert the following to the bootorder.txt and include it in the build process (see make menuconfig).

/pci@i0cf8/*@1f,2/drive@0/disk@0 HALT /pci@i0cf8/usb@1d/hub@1/storage@1/*@0/*@0,0 /pci@i0cf8/usb@1d/hub@1/usb-*@1 /pci@i0cf8/*@1f,2/drive@1/disk@0 /pci@i0cf8/pci-bridge@1c/*@0 /rom@img/tint /rom@img/coreinfo

Leave a Reply